**BITFLIP - Accueil & Introduction**

19 nov. 2025 09h25

Réfectoire

**Régis LEVEUGLE**

Professor Grenoble INP – UGA

TIMA Laboratory

**Digital integrated systems' hardening by design: from Reliability and Safety goals to Security, Pitfalls and Challenges**

European Cyber Week - The Sovereign Cyber & Defence AI forum, Rennes, France, November 17-20, 2025

**Digital integrated systems' hardening by design: from Reliability and Safety goals to Security**

**Pitfalls and challenges**

**R. Leveugle**

**TIMA Laboratory**

Grenoble INP - Graduate schools of Engineering and Management

Univ. Grenoble Alpes

France

**TIMA**  R. Leveugle, TIMA / AMfoRS

**Context – Pervasive integrated (digital) systems**

- An increasingly large panel of application areas ...

- ... with very different constraints (computation or service complexity and requirements, power/energy efficiency, computation power, acceptable costs, time to market, ... sources of disturbance and threats, trustworthiness => dependability)

**TIMA**  R. Leveugle, TIMA / AMfoRS

**Dependability?**

- Notion of service**

- Ability to deliver service that can **justifiably be trusted** (=> user confidence, validation/characterization ...)

- Correct when it implements the intended/specified system function

- Dependability: alternate definitions**

- Ability to deliver service that can **justifiably be trusted** (=> user confidence, validation/characterization ...)

- Ability to avoid service failures that are more frequent or more severe than is acceptable to the user(s)

- No absolute property**

A. Avizienis, J. C. Laprie, B. Randell, "Dependability and its threats: a taxonomy", 18th IFIP World Computing Congress, Topical day 3 "Fault Tolerance for Trustworthy and Dependable Information Infrastructures", Toulouse, France, August 23-24, 2004, pp. 91-120

**TIMA**  R. Leveugle, TIMA / AMfoRS

**Various concerns ...**

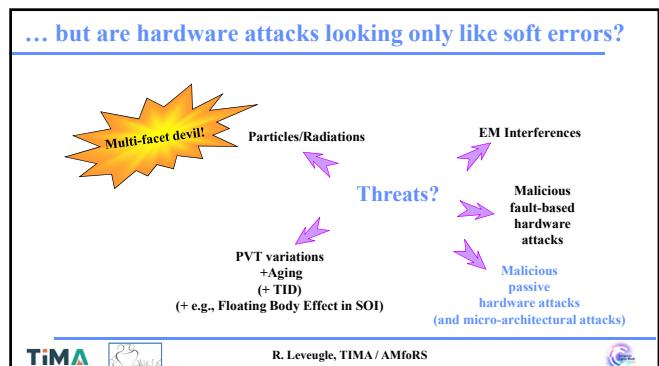

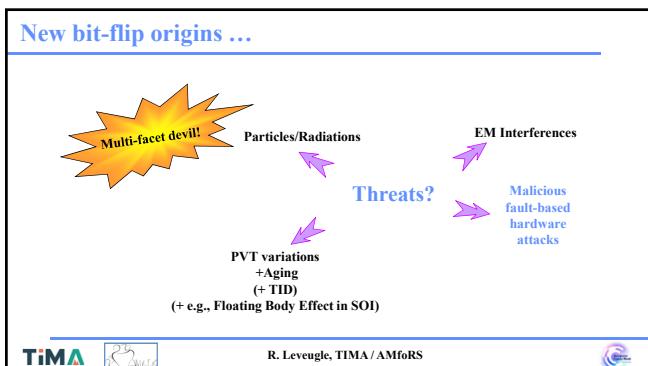

The dependability of our systems is a major concern ...

... but all electronic systems are at risk due to components (un)reliability and then ...

**Bit-flips** **Soft errors** (transient errors, remanent errors) => SDCs/SDEs, ...

**SEUs**

**Particles/Radiations**

**EM Interferences**

**Threats?**

**Multi-facet devil!**

**Not (yet) the whole landscape**

... so protections are needed for trustworthiness! => Hardening by design

**TIMA**  R. Leveugle, TIMA / AMfoRS

**Bit-flips history, episode 1: particles/radiations**

- SEUs in electronics first described during above-ground nuclear testing (1954-1957)

- Then in the 1970s ...

- First SEU paper about Hughes satellite in the IEEE Trans. on Nuclear Science in 1975

D. Binder, E. C. Smith and A. B. Holman, "Satellite Anomalies from Galactic Cosmic Rays," in *IEEE Transactions on Nuclear Science*, vol. 22, no. 6, pp. 2675-2680, Dec. 1975, doi: 10.1109/TNS.1975.4328188.

- ... but the term was first adopted in 1979

C. S. Gausez, E. A. Woldrich and R. G. Allas, "Single Event Upset of Dynamic RAMs by Neutrons and Protons," in *IEEE Transactions on Nuclear Science*, vol. 26, no. 6, pp. 5048-5052, Dec. 1979, doi: 10.1109/TNS.1979.4330270.

- First record of SEU on Ground: Cray-1 Computer at Los Alamos in 1976

E. Normand et al., "First Record of Single-Event Upset on Ground, Cray-1 Computer at Los Alamos in 1976," in *IEEE Transactions on Nuclear Science*, vol. 57, no. 6, pp. 3114-3120, Dec. 2010, doi: 10.1109/TNS.2010.2083687.

- First evidence of soft errors from alpha particles in packaging materials in 1978

T. C. May and M. H. Woods, "A New Physical Mechanism for Soft Errors in Dynamic Memories," 16th International Reliability Physics Symposium, San Diego, CA, USA, 1978, pp. 33-40, doi: 10.1109/IRPS.1978.262815.

**TIMA**  R. Leveugle, TIMA / AMfoRS

## Dependability: historical evolution (attributes)

- Once upon a time ...

- Unreliable components ...

- ... then harsh environments

- Increasing use of electronics in critical applications

=> Reliability

Continuous correct service => Fault Tolerant Computing domain

=> Availability

Probability of correct service at a given time => Maintainability

=> Safety

Avoidance of catastrophic events

May be antagonistic with availability

**TiMA** R. Leveugle, TiMA / AMfoRS

## Beyond natural (external) perturbations?

**TiMA** R. Leveugle, TiMA / AMfoRS

## And then ...

**TiMA** R. Leveugle, TiMA / AMfoRS

## From another world ... security!

- Once upon a time ...

- Context of computer networks and software (malware)

- Concerns limited to information integrity and loss

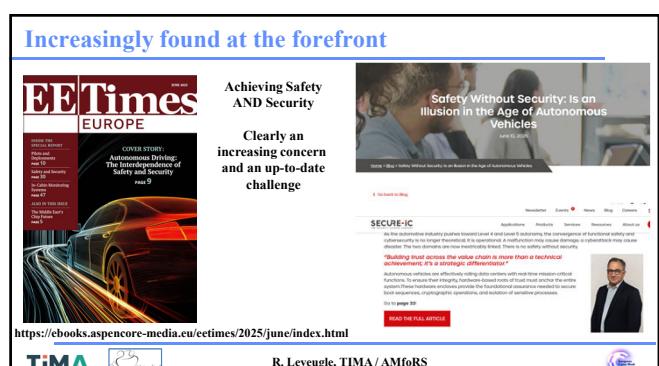

- Widespread concerns

- Security can be today one pillar (or prerequisite) for safety in many systems

- Mission loss can be (at least) as critical as information loss

- Since about two decades ... need for Resilience (i.e. robustness)

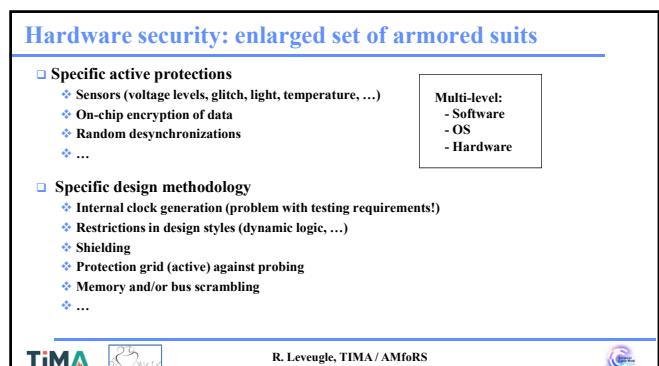

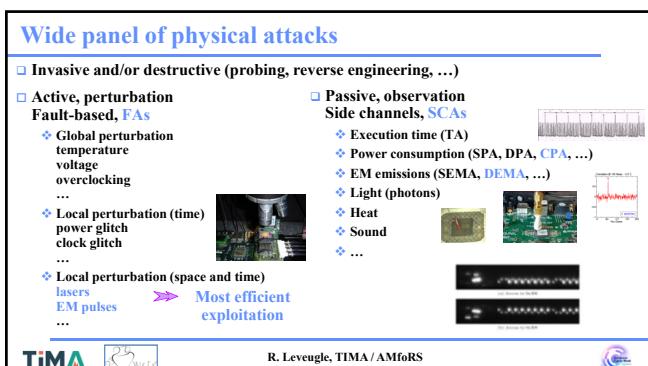

- Physical attacks on systems (from smartcard to IoT devices and everything ...) => Hardware security

- ... usually with physical access to the devices ... but extended to remote attacks ...

- Can be leveraged in a second step to perform remote attacks with wide impact => must not be neglected!

**TiMA** R. Leveugle, TiMA / AMfoRS

## Bit-flips history, episode 2: towards security concerns

- Seminal paper by Boneh et al. (1997) showed that faults can be catastrophic for cryptosystems – fault attack on RSA deciphering engine

D. Boneh, R.A. DeMillo, R.J. Lipton, "On the importance of checking cryptographic protocols for faults," in: Fumy W (ed) Advances in cryptology – EUROCRYPT'97, International Conference on the Theory and Application of Cryptographic Techniques, Konstanz, 11–15 May, 1997, Lecture notes in computer science, vol 1233, Springer, pp 37–51, doi: 10.1007/3-540-49053-0\_4.

- Another reference paper on early fault attack on RSA

M. Joye, A.K. Lenstra, J.J. Quisquater, "Chinese remaindering cryptosystems in the presence of faults," Journal of Cryptology, Vol.12, pp.241–245, 1999.

- New security threat: bit-flip(s) ... often assumed as "single" in early literature

=> "Bellcore attack"

**TiMA** R. Leveugle, TiMA / AMfoRS

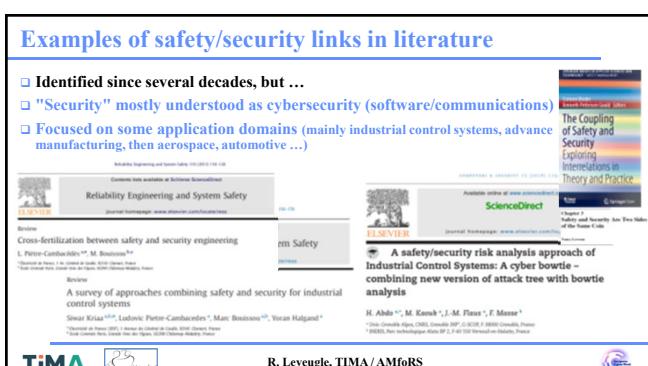

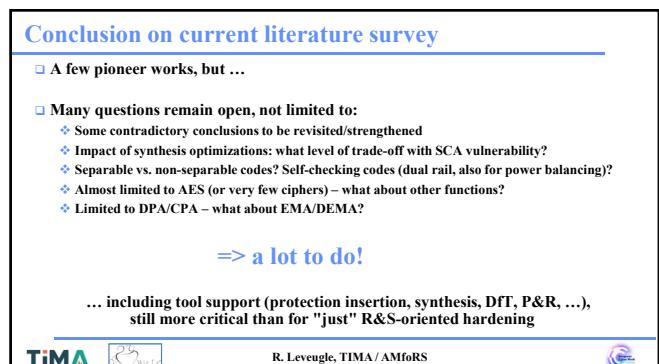

## Security vs. Reliability/Safety

- ❑ Different communities, different backgrounds, most often different teams in industry

- ❖ No unique terminology (and depends on the application domain)

- ❖ Difficulty of communication and identification of common or conflicting concerns

- ❑ Most often, hardening tasks are tackled separately

- ❑ In the literature, contributions are most often focused on one aspect (and even a subset!)

### Question:

Are R&S-oriented design hardening measures

beneficial from the security point of view,

and up to what extent?

R. Leveugle, TiMA / AMfORS

## Several sub-questions

- ❑ Are R&S-oriented design hardening measures sufficient for security (at least to counter fault attacks)?

- ❑ Are design for R&S and design for security just complementary?

- ❑ Is hardening against faults always beneficial for security?

- ❑ ...

R. Leveugle, TiMA / AMfORS

## Are R&S-oriented design hardening measures sufficient for security (at least to counter fault attacks)?

R. Leveugle, TiMA / AMfORS

## Functional safety – many standards

### Functional Safety Standards

And:

IEC 62279 - Railways

ISO 13849 - Machinery

...

Functional safety:

absence of unreasonable risk

due to hazards caused by malfunctioning

behavior of electrical/electronic systems

Standards include

best practices

AND robustness level

requirements

e.g., ASIL A to D in

ISO 26262

=> Hardening by design

e.g., dual core lockstep for ASIL-D

R. Leveugle, TiMA / AMfORS

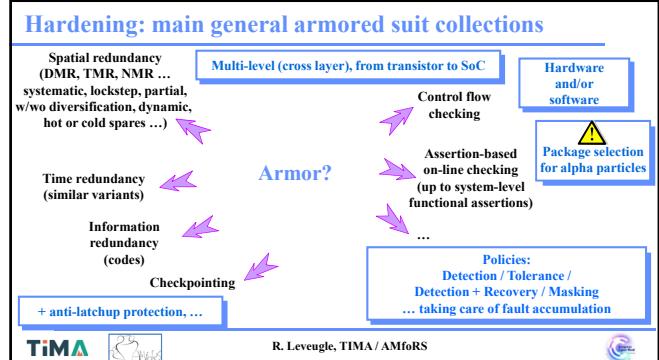

## Hardening against faults – assume job done for R&S!

- ❑ And then ... security! Dream or nightmare?

### From usual literature ...

Job is done for FAs!

"Just" add SCA countermeasures

(methods will not be detailed in this talk)

### Observation on state-of-the-art literature:

Large majority of studies dealing with

either FA or SCA (exclusively)

Assuming FA and SCA fighting are two

independent (fully complementary) jobs

R. Leveugle, TiMA / AMfORS

## Hardening against faults – assume job done for R&S!

- ❑ And then ... security! Dream or nightmare?

### From usual literature ...

Job is done for FAs!

"Just" add SCA countermeasures

(methods will not be detailed in this talk)

### In fact ... not so simple!

Is the protection sufficient to counter all FAs

(or limited percentage)? What fault model(s)?

Efficiency of combining several

countermeasures?

What about the level of leaks? Would SCA

sensitivity be worsen?

(+ specific security armors)

...

R. Leveugle, TiMA / AMfORS

**Hardening for R&S is NOT sufficient to counter all FAs!**

IEEE Xplore® [Browse](#) [My Settings](#) [Help](#) [Institutional Sign In](#)

Conferences > 2017 Workshop on Fault Diagn... [View](#)

**Safety != Security: On the Resilience of ASIL-D Certified Microcontrollers against Fault Injection Attacks**

Publisher: IEEE [Cite This](#) [PDF](#)

Nils Wiersma ; Ramiro Pareja [All Authors](#)

**TiMA**  R. Leveugle, TiMA / AMfoRS

## Threat characteristics: fault models to be revisited

- **Reliability and Safety**

- ❖ Natural events, "Hazards"

- ❖ Unintentional

- ❖ Pre-determined behavior (physics)

- ❖ Thoroughly analyzed and modeled

- ❖ Often a low occurrence rate

- ❖ One-shot

- ❖ General context rather stable, established fault models

- **Security**

- ❖ Attacks

- ❖ Intentional, malicious

- ❖ Multiple ways to reach the goal, New attacks everyday

- ❖ Multiple trials, hacker learning curve

- ❖ Statistical approaches cannot easily be adopted for characterization (too little data shared in real time)

- ❖ Specific equipments (nuisance capacity larger than natural events)

**TiMA**  R. Leveugle, TiMA / AMfoRS

**Are design for R&S and design for security just complementary?**

**Is hardening against faults always beneficial for security?**

**Secure composability of different attack countermeasures**

**TiMA**  R. Leveugle, TiMA / AMfoRS

**"Security paradox":**

**where attempts to strengthen security against some attacks can actually weaken the overall security of the system**

**TiMA**  R. Leveugle, TiMA / AMfoRS

**Already identified in 1999-2002 (algorithm level)**

**□ Joye's Observability Analysis**

Observability Analysis

– Detecting When Improved Cryptosystems Fail –

[Published in B. Preneel, Ed., *Topics in Cryptology – CT-RSA 2002*, Lecture Notes in Computer Science, pp. 17–29, Springer-Verlag, 2002.]

Marc Joye<sup>1</sup>, Jean-Jacques Quisquater<sup>2</sup>, Sung-Ming Yen<sup>3,4</sup>, and Moti Yung<sup>5</sup>

<sup>1</sup> Gemplus Card International, Card Security Group, Gif-sur-Yvette, France

<sup>2</sup> UCL Crypto Group, Louvain-la-Neuve, Belgium

<sup>3</sup> UCL Crypto Group, Louvain-la-Neuve, Belgium

<sup>4</sup> Dept. of Computer Sciences, National Central University, Taiwan, R.O.C.

<sup>5</sup> Princeton University, Princeton, NJ, U.S.A. – <http://www.cs.princeton.edu/~moti/> – <http://www.cs.nccu.edu.tw/~moti/>

**Before:**

M. Joye et al., "Security paradoxes: how improving a cryptosystem may weaken it", National Conf. on Information Security, Taichung, Taiwan, May 1999

M. Joye, J.-J. Quisquater, S.-M. Yen, M. Yung, "Observability analysis: Detecting when improved cryptosystems fail PDF", In B. Preneel, Ed., *Topics in Cryptology – CT-RSA 2002*, vol. 2271 of Lecture Notes in Computer Science, pp. 17–29, Springer-Verlag, 2002.

**TiMA**  R. Leveugle, TiMA / AMfoRS

**Error detection is leaking secrets**

**□ First Joye's paradox on RSA computations: an identified error (leading to an error message ending the encryption) allows inferring the value of the secret key without choosing plaintexts and ciphertexts, so allows successful attacks under weaker assumptions than without detection ("oracle" – differences in system behavior can be observed, leaking information on inner workings)**

**□ Similar to "safe-error" hardware attacks: undetected errors (or errors not modifying the final result) leak inner data values**

- ❖ Simple example: forcing a secret bit at a given value with/without impact on the result leaks the value the bit had

- ❖ Other case: used/unused modified data can leak the executed branch of a program, thus the condition value

**□ Re-computing after detection is not a solution: it is revealed by a timing analysis**

**□ Behavior observation but ... What about other leaks?**

**TiMA**  R. Leveugle, TiMA / AMfoRS

## Interlude - Enlarged view: beyond error management ...

- ❑ Same kind of paradox in other contexts

- ❑ Other protections can lead to new (or easier) attacks ...

### ❑ Example: concerns with supply chain and outsourcing of manufacturing to (untrustworthy) offshore foundries

- ❖ Trojan insertions

- ❖ Cloning (counterfeiting) / over-production

- ❖ One answer? Logic locking (secret key inputs)

M. T. Rahman, S. Tajik, M. S. Rahman, M. Tehranipour, and M. S. Hossain, "A Fault Analysis of Logic Locking and the Inappropriate Security Assumption of Logic Locking Schemes," IEEE Int. Symposium on Hardware Oriented Security and Trust (HOST), San Jose, CA, USA, 2020, pp. 262-272.

❖ But ... limitation (key recovery by SCA) and LEDFA (Locking-Enabled DFA): DFA on incorrectly unlocked cryptographic circuits can be simpler than on regular circuits without logic locking

D. Upadhyaya, M. Gay, I. Polian, "Locking-Enabled Security Analysis of Cryptographic Circuits," Cryptography, 2024; 8(1):2

R. Leveugle, TiMA / AMfoRS

## Protecting assets

- ❑ Looking at the weaker link in the chain ... even if not the most easily accessible

- ❑ Any vulnerability, or decrease in resistance, even patched, can help intrusion

- ❑ Most often neglected in the literature in the context of FA fighting (not saying it is unknown ...)

R. Leveugle, TiMA / AMfoRS

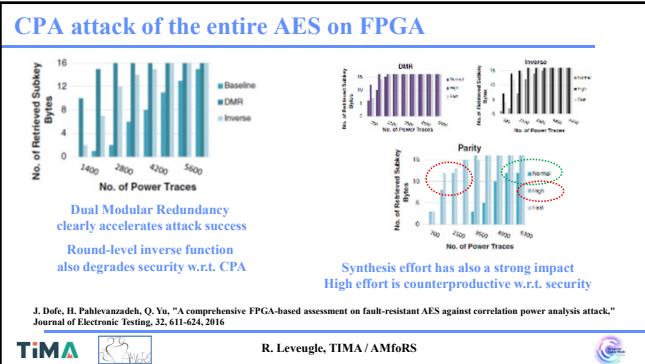

## Worst point: fighting FAs can reduce SCA fighting efficiency

- ❑ Little existing literature ... Starting point at TiMA (2006-2009 ... V. Maingot thesis)

### ❑ Then

- ❖ From 2007 - F. Regazzoni (Lugano, Switzerland), T. Eisenbarth (Bochum, Germany), L. Breveglieri (Milano, Italy), P. Renne (EPFL, Lausanne, Switzerland), I. Koren (Amherst, USA)

- ❖ 2009 - J. Dai and L. Wang (Connecticut, USA)

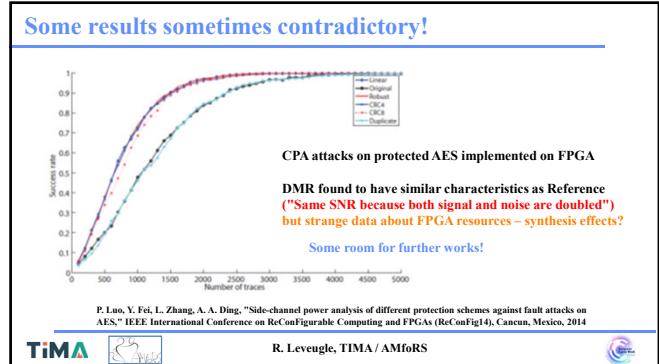

- ❖ 2014 - P. Luo et al. (Boston, USA)

- ❖ 2016 - H. Pahlevanzadeh, J. Dofe, and Q. Yu (New Hampshire, USA)

- ❖ 2017 - J. Riha, V. Miskovsky, H. Kubatova, and M. Novotny (Prague, Czech republic)

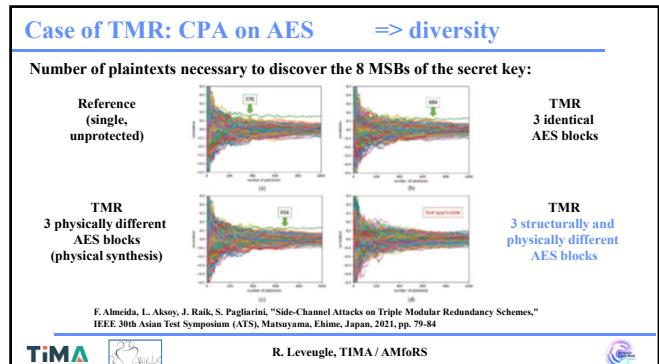

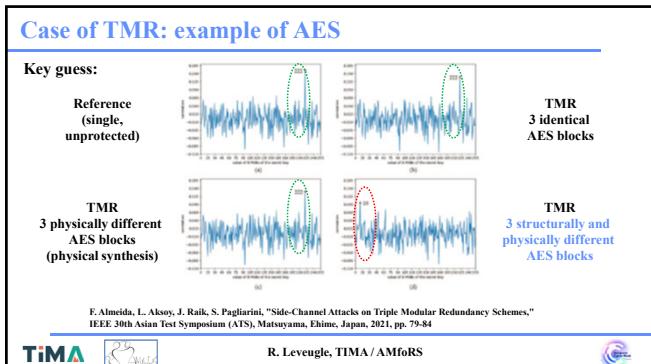

- ❖ 2021 - F. Almeida, L. Aksoy, J. Raik, and S. Pagliarini (Tallinn, Estonia)

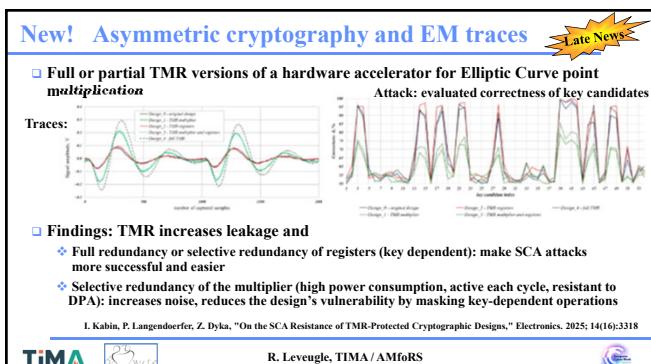

- ❖ 2025 - I. Kabin, P. Langendoen, and Z. Dyka (IHP Frankfurt & Cottbus, Germany)

R. Leveugle, "Embedded tutorial: Integrated system hardening seen from a security point of view: dream or nightmare?" IEEE Latin American Test Symposium (LATs), San Andrés Island, Colombia, March 11-14, 2025

R. Leveugle, TiMA / AMfoRS

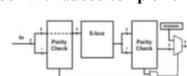

## Main subjects covered in previous studies

- ❑ Mainly on register or AES (Sbox + register, then full AES) case study

- ❑ From gate level ... to transistor level ... to FPGAs

- ❑ From DPA ... to CPA

- ❑ From error detecting/correcting codes ... to DMR / TMR ...

TiMA S2VLSI

R. Leveugle, TiMA / AMfoRS

## Interlude – Is cryptography the only relevant context?

- ❑ Pervasive development of AI-powered embedded systems

- ❑ Also in critical domains, from automotive to defence (see ECW program!) and many others

### ❑ Attacks on neural networks: no secret key to find, but ...

- ❖ Fault attacks

- Global misclassifications: model accuracy reduction, system efficiency decrease

- Selective misclassifications of a specified input pattern into an adversarial class

- Extraction of Embedded Neural Network Models

- ❖ SCA attacks

- Retroengineering, architecture and parameter extraction

- Mimic a system with a substitute model, even with a limited access to similar training data

Batina, L., Bhasin, S., Breier, J., Hou, X., Jia, D. (2022). On Implementation-Level Security of Edge-Based Machine Learning Models. In: Batina, L., Böck, T., Buhai, L., Pieck, S. (eds) Security and Artificial Intelligence. Lecture Notes in Computer Science, vol 13049. Springer, Cham.

R. Leveugle, TiMA / AMfoRS

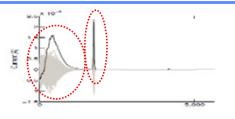

## Kocher's DPA attack on AES S-box

### Reference implementation of the AES S-box

### AES S-box with added complementary parity

Attack tuning matters!

F. Regazzoni, L. Breveglieri, P. Renne, I. Koren, "Interaction Between Fault Attack Countermeasures and the Resistance Against Power Analysis Attacks," In: Joye, M., Tunstall, M. (eds) Fault Analysis in Cryptography. Information Security and Cryptography. Springer, Berlin, Heidelberg, 257-272, 2012

TiMA S2VLSI

R. Leveugle, TiMA / AMfoRS

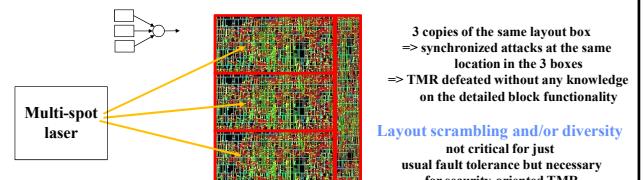

## ... and concerns are not limited to FAs vs. SCAs

- More concerns related to implementation ...

- Recall: attack equipments can induce more nuisance than natural causes

- Usual hardware space redundancy at risk => P&R obfuscation

- Usual time redundancy at risk => time distribution obfuscation

Other motivations for diversity!

... at the expense of costs and TTM

TiMA

R. Leveugle, TiMA / AMfoRS

## Multi-point injections: setup example, 2 independent points

ALPhANOV

Centre Technologique Optique et Laser

PRODUITS & SERVICES • SOLUTIONS LASER POUR LE TEST DE CIRCUITS INTEGRÉS

Injection de fautes laser double spots

- D-LMS

<https://www.alphanov.com/produits-services/injection-de-fautes-laser-double>

R. Leveugle, TiMA / AMfoRS

TiMA

## Multi-point injections: setup example, 4 independent points

<https://www.errol-laser.com/smart-cart-laser-bench>

[https://www.errol-laser.com/\\_files/ngd/1cf6d8e\\_1e3b0623c454f02b125e891cd53a245.pdf](https://www.errol-laser.com/_files/ngd/1cf6d8e_1e3b0623c454f02b125e891cd53a245.pdf)

TiMA

R. Leveugle, TiMA / AMfoRS

## Exploiting multi-injections with lasers

IEEE Xplore® Browse My Settings Help Institutional Sign In

Conferences > 2010 Workshop on Fault Diagno... SPRINGER NATURE Link

Multi Fault Laser Attacks on Protected CRT-RSA SPRINGER NATURE Link

Published: IEEE Cite This PDF

Elena Trichina, Roman Korkikyan, All Authors

TiMA

R. Leveugle, TiMA / AMfoRS

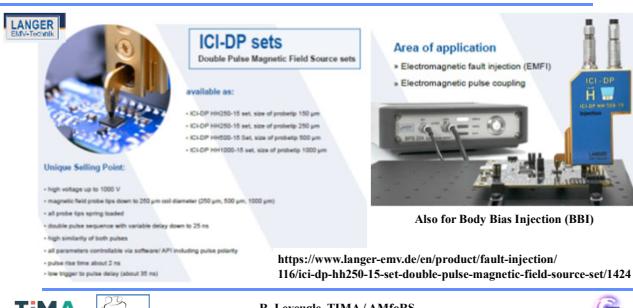

## Also available for EMFI, sequence of 2 pulses

<https://www.langer-envi.de/en/product/fault-injection/116/ici-dp-hh250-15-set-double-pulse-magnetic-field-source-set/1424>

TiMA

R. Leveugle, TiMA / AMfoRS

## Impact on space redundancy

- Malicious, with 4-spot laser station => multiple spatial faults impossible after natural events can be induced

- Identification can be made easier with today's AI-based techniques

TiMA

R. Leveugle, TiMA / AMfoRS